## **Technical Information**

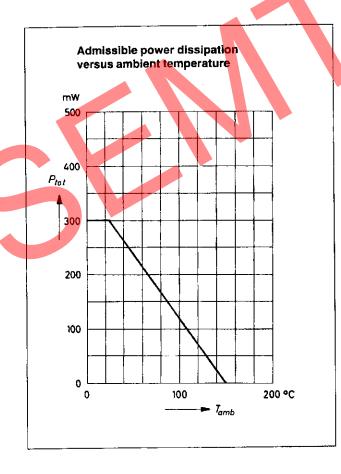

#### **Admissible Power Dissipation**

The indicated maximum admissible junction temperature must not be exceeded because this could damage or cause the destruction of the transistor crystal. Since the user cannot measure this temperature, data sheets also reveal the maximum admissible power dissipation  $P_{\text{tot}}$  usually in the form of a derating curve (see diagram).

If power dissipation is kept within these limits the maximum junction temperature will not be exceeded. This can easily be checked by using the equation.

$$T_i = T_{amb} + P_{tot} \cdot R_{th}$$

For the thermal resistance  $R_{\rm th}$  the junction to ambient thermal resistance  $R_{\rm thA}$  is usually substituted in the case of small transistors (in the TO-18 or TO-92 package). In the case of power transistors (in the TO-202 or similar packages) which are usually mounted on a cooling fin or heat sink for the purpose of heat dissipation, the sum of the junction to case thermal resistance  $R_{\rm thC}$  plus the heat sink to ambient thermal resistance  $P_{\rm thS}$  plus - for more accurate calculations - the mounting surface to heat sink thermal resistance is substituted for the thermal resistance in this equation. In order to keep the mounting surface to heat sink thermal resistance low, a heat conducting compound (silicone grease) is to be applied to the mounting surface before the transistor is screwed on. If a mica insulation is used, the thermal resistance of the mica washer must be added which amounts to about 0.5 K/W.

Directors for determining the thermal resistance  $R_{\rm ths}$  for cooling fins can be found on page 6.

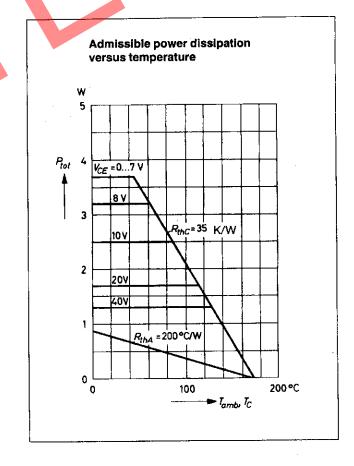

Since the distribution of heat in the transistor crystal is not uniform and depends on voltage and current, some transistors are accompanied by derating curves showing  $P_{tot}$  as a function of  $T_{c}$  and  $T_{amb}$  with the collector voltage  $V_{CE}$  as parameter (see diagram below).

# SEMTECH ELECTRONICS LTD.

(Subsidiary of Semtech International Holdings Limited, a company listed on the Hong Kong Stock Exchange, Stock Code: 724)

### **Technical Information**

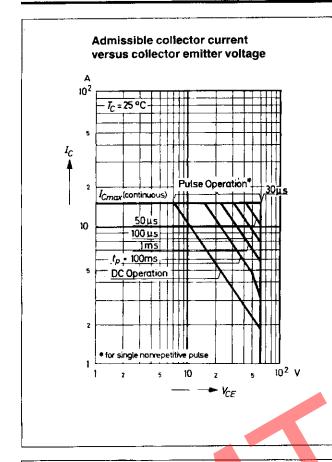

For some power transistors the data sheets also contain a diagram giving "admissible collector current" or "permissible operating range" which gives further information on admissible power dissipation. One example is illustrated in the diagram left.

These diagrams are based on continuous power dissipation. However, pulse power dissipation may usually exceed continuous power dissipation. To ascertain maximum admissible pulse power dissipation  $P_{th}$ , reference is made to the pulse junction to case thermal resistance  $r_{th}$  or the pulse junction to ambient thermal resistance  $r_{th}$  whose value can be derived from the  $r_{th} = f(t_p)$  diagram below.

Use the equation

$$T_i = T_{amb} + P_1 \cdot r_{thA}$$

or, if the continuous power dissipation  $P_0$  is to be taken into consideration:

$$T_i = T_{amb} + P_0 \cdot R_{thA} + P_i \cdot r_{thA}$$

If the transistor is mounted on a cooling fin then the equation becomes:

$$T_i = Tamb + P_{tot} \cdot R_{ths} + R_i \cdot r_{thc}$$

wherein P<sub>tot</sub> is the mean value of the pulse power dissipation P<sub>i</sub>. Where continuous power dissipation must be considered in addition, the equation is expanded accordingly:

$$T_i = T_{amb} + P_{tot} \cdot R_{thS} + P_D \cdot R_{thC} + P_1 \cdot r_{thC}$$

wherein Ptot is the mean value of the total power dissipation.

The thermal resistance and pulse thermal resistance values derived from the data sheets apply without limitation only to small collector emitter voltages  $V_{\text{CE}}$ , between about 5 and 10V. For higher voltages these thermal resistance values have to be multiplied by a correction factor  $K_{\text{V}}$  which has to be calculated from the previously mentioned derating curves. The admissible power dissipation  $P_{\text{tot max}}$ , applicable to low collector voltages, must be divided by the admissible power dissipation  $P_{\text{tot V}}$  for the higher collector voltage V:

$$K_v = \frac{P_{tot \, max}}{P_{tot \, v}}$$

The complete equation for T<sub>i</sub> then reads:

$$T_{l} = T_{amb} + P_{tot} \cdot R_{thS} + P_{D} \cdot K_{V} \cdot R_{thC} + P_{L} \cdot K_{V} \cdot r_{thC}$$

## SEMTECH ELECTRONICS LTD.

(Subsidiary of Semtech International Holdings Limited, a company listed on the Hong Kong Stock Exchange, Stock Code: 724)